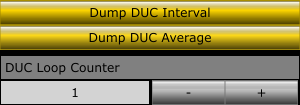

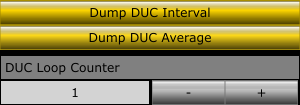

The 'Dump DUC Interval' and 'Dump DUC Average' Buttons

- These outputs are only active when in transmit mode.

- The 'DUC Loop Counter' must be >= 1 for these buttons to cause output.

- The value of this counter sets the period of the average output.

The 'Dump DUC Average' button causes this line to be displayed:

timeEachDUCPacket(): 170.055082971 - 1.000100603, average: 0.000937166, median: 0.000013075, minimum: 0.000002097, maximum: 0.054570096

The values are the intervals between arrival of DUC packets,

calculated over 'DUC Loop Counter' period.

- Fields:

- output label.

- seconds since Athena started.

- length in seconds of this loop.

- average interval during the period.

- median interval during the period.

- minimum interval during the period.

- maximum interval during the period.

If the 'Dump DAC Average' button is active, the 'Dump DUC Interval' button causes these lines to be displayed:

TIME: 0304: 0.000009725

TIME: 0305: 0.000007925

TIME: 0306: 0.000009602

TIME: 0307: 0.000007637

TIME: 0308: 0.000007615

...

The DUC Loop Counter causes this line to be displayed:

ducDataLoop(): 170.055082971 - 1.000100603, another 192K * 1 samples (1440)

- Fields:

- output label.

- seconds since Athena started.

- length in seconds of this cycle.

- summary.

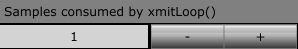

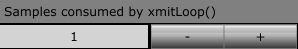

The 'Samples consumed by xmitLoop()' Slider

When > 0, this slider shows the time required to receive the

(192K * period) samples used for DAC output over the period in seconds set with the slider.

When active, these lines are displayed:

xmitLoop(): 13021.677069953 - 0.997236063, another 192K * 1 samples

xmitLoop(): 13022.724890479 - 1.047801323, another 192K * 1 samples

xmitLoop(): 13023.681445013 - 0.956535655, another 192K * 1 samples

...

- Fields:

- output label.

- seconds since Athena started.

- length in seconds of this cycle.

- summary.

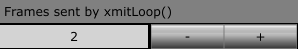

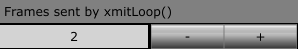

The 'Frames sent by xmitLoop()' Slider

When > 0, this slider shows the (15000 * period) frames sent to the

DAC over the period in seconds set with the slider.

When active, these lines are displayed:

sendNextFrame(): 16048.822593175 - 1.999950025, another 15000 * 2 frames

sendNextFrame(): 16050.822795404 - 2.000184008, another 15000 * 2 frames

sendNextFrame(): 16052.822851159 - 2.000035602, another 15000 * 2 frames

...

- Fields:

- output label.

- seconds since Athena started.

- length in seconds of this cycle.

- summary.

The 'DAC Frame Counter' Slider

When > 0, this slider dumps statistics about the DAC frame

buffering levels over the period in seconds set with the slider.

When active, these lines are displayed:

sendDAC(): 41.395563063 firstFrameCount: 1269, lastFrameCount: 1390, average: 1002, median: 1007, minimum: 296, maximum: 1687, minMinimum: 338

sendDAC(): 44.394337001 firstFrameCount: 1389, lastFrameCount: 934, average: 1016, median: 1025, minimum: 366, maximum: 1698, minMinimum: 296

sendDAC(): 47.394957471 firstFrameCount: 933, lastFrameCount: 1054, average: 1012, median: 1020, minimum: 334, maximum: 1590, minMinimum: 296

...

- Fields:

- output label.

- seconds since Athena started.

- number of buffered frames at the start of the transmit period.

- number of buffered frames at the end of the transmit period.

- average number of buffered frames during the transmit period.

- median number of buffered frames during the transmit period.

- minimum number of buffered frames during the transmit period.

- maximum number of buffered frames during the transmit period.

- minimum of all minimums recorded since Athena was started.

The 'DAC Frame Prefill' Slider

The 'DAC Frame Prefill' slider sets the value of a prefill

counter used when starting a transmit sequence. It causes

this many frames to be sent at the start of the transmit sequence to

ensure the FPGA has enough samples buffered to prevent under-run.

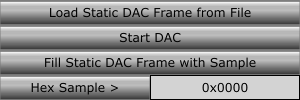

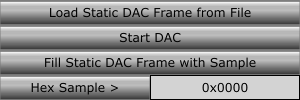

The 'Load, Start, Fill' Buttons and 'Hex|Decimal Sample >' Slider

The 'Load Static DAC Frame from File' button pops up a file

chooser window, allowing the load of the frame from a file.

The 'Start DAC' button causes the static frame to be sent to the

DAC every time a frame is received from the ADC.

The 'Fill Static DAC Frame with Sample' button fills the output frame with

repeated copies of the current 'Hex|Decimal Sample'.

The 'Hex|Decimal Sample' button switches between hex and decimal

display of the sample.

The sample entry box allows you to define a int16_t

sample for use by the 'Fill Static DAC Frame with Sample' button. Entries starting

with '0x' are parsed as hex, otherwise they are parsed as decimal.

The 'Bit Bucket' Button

The 'Bit Bucket' button causes the sample packets to be sent to

a non-existant IP address. Since they are UDP packets, they are

sent out the NIC, and can be examined with wireshark. Since

they wont actually reach the hardware, any existing bugs in FPGA

firmware wont be ticked.

The '__[LITTLE|BIG]__ENDIAN__ Samples' Button

The '__[LITTLE|BIG]_ENDIAN__ Samples' button causes the real

int16_t samples to be sent in either little or big endian

format.

It does not affect the endian-ness of either static

samples or static frames.

The 'Panic' Button

The 'Panic' button stops the running ADC, sets the drive level to

0, sleeps a short time, then restarts ADC 0.

This sometimes, but not always, returns the system to a

functional state after the FPGA wedges from the xmit packet

bug...

Other times you need to restart Athena from scratch...